便利な日常生活のあらゆる場面を支える高周波(RF)技術 | TECH+ マイナビニュース マイナビ

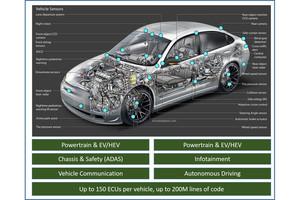

図1:アナログ/RF/ミクスドシグナル・アプリケーション

ナノメートル回路におけるRF検証の課題

プロセスの微細化には、ローパワー化や高性能化など多くのメリットがありますが、ナノオーダーのCMOSテクノロジを使用するRF設計者は、電圧レベルの低下による回路の非線形性やデバイスノイズへの影響など、設計の複雑化によって生じる課題に対応しなければなりません。

設計が複雑になる要因として、抵抗や容量の寄生が大幅に増加することが挙げられます。このため、レイアウトが及ぼす影響を含まない回路図デザインをそのまま単純にシミュレーションしてしまうと、デザインの正確なアナログモデルが表現されないという大きなリスクを伴い、結果としてポストレイアウト・シミュレーションの課題が大きくなります。

このように複雑な設計を行うには、デジタル・キャリブレーションや補正技術を採用したり、初期設計段階からレイアウトを組み込んで性能や消費電力を最適化したりする必要があります。そのため、テープアウト前の最終的な設計サインオフを行うには、プロセスミスマッチ、電圧、温度変化のほか、電力、周波数、ビット調整を行うためのレイアウトの影響やRF解析を含めた包括的な検証計画が必要となります。

RF回路設計における設計と検証の課題を克服するために、最新のRFシミュレータエンジンでは、回路の線形性、ノイズ、ゲインを検証する2つの解析手法が使われるようになっています。1つは、タイムドメインに基づくシューティングニュートン(SN)法であり、もう1つは、周波数ドメインに基づくハーモニックバランス(HB)法です。それぞれの手法は、対象となる特定のアプリケーションに合わせて最適化されています。SN法は、すべての周期的回路、特に急激な変化の非線形時間波形を伴う回路に適しています。HB法は、高い線形性から中程度の非線形歪曲があり、広いダイナミックレンジが必要な、Sパラメータでモデリングされた周波数ドメインモデルを使用する回路に最適です。

現在使われている先進的なトランシーバの設計では、トーンの周波数が異なる2つ以上の周期信号を回路に印加するマルチトーン・シミュレーションの実施が一般的です(図2)。これらのシミュレーションは、トーン間隔が狭いためにタイムドメインでの扱いが難しく、最小時間ステップを最高周波数に対応させる必要があるために非常に時間がかかります。ハーモニックバランス解析は、複数の入力周波数を持つ回路のシミュレーションを実用的な形で実現します。周波数スペクトラムがスパースな場合、マルチトーン・ハーモニックバランス・シミュレーションは、タイムドメインのアプローチと比較して、より高速で、より少ないメモリで、より高い精度で実行できます。マルチトーン・シミュレーションの実行時間は、回路サイズやトーン数など、いくつかの要因に影響されます。例えば、2次、3次IM積(IM2、IM3)などの相互変調歪みの影響を正確に把握するために、1トーンのシミュレーションから3トーンのシミュレーションに移行する場合、精度を確保するために相互変調項の数を増やさなければなりません。その結果、シミュレーション時間が9倍に跳ね上がることもあり、場合によっては、マルチスレッドソルバとモデル評価の最新技術を搭載した最先端のシミュレーションエンジンを使用しない限り、レイアウト後のデザインが使い物にならないといった状況に陥りかねません。これは特に、最先端ノードのFinFETでの設計に当てはまります。

ナノオーダーの回路に対応したRF検証プラットフォーム

Analog FastSPICE(AFS)は、シューティングニュートン(SN)エンジンだけでなく、シングルトーンとマルチトーン両方のハーモニックバランス(HB)、ノイズ(HBNOISE)、AC(HBAC)、安定性(HBSTB)、散乱パラメータ(HBSP)、伝達関数(HBXF)解析に対応したハーモニックバランス(HB)エンジンを提供します。また線形および線形に近い回路で求められる精度と性能を提供するために、AFSハーモニックバランス・ソルバは、自動インテリジェンスアルゴリズムによって、精度を犠牲にすることなく、性能と収束をさらに最適化させています。

AFSのハーモニックバランス(HB)解析は、Analog FastSPICEプラットフォームの一部として、追加費用なしで既存顧客に提供されます。AFSプラットフォームは、世界の主要ファウンドリによってその精度が認定されており、従来のSPICEシミュレータに比べて5倍以上、並列SPICEシミュレータに比べて2倍以上のナノメータSPICE精度を実現しています。さらに、最近発表された大規模ポストレイアウト設計をナノメータ単位で検証するAnalog FastSPICE eXTremeテクノロジでは、前世代比で最大10倍の性能向上を実現します。

AFSプラットフォームは、50M以上の素子容量と、Symphonyによる混合信号シミュレーションを提供します。シリコンの正確な特性評価のために、AFSプラットフォームには、包括的フルスペクトル・デバイスノイズ解析が含まれています。またSolido Variation Designerと統合することで、バリエーションを考慮した設計カバレッジを、少ないシミュレーション回数で、従来の総当たり方式に匹敵する精度を実現します。

ナノメータRF回路の設計には、広範なスイープ、コーナー、モンテカルロ解析が必要です。AFS HBは、マルチスレッド機能を利用することで、シングルコア実行以上の高速な性能を実現します。AFSプラットフォームは、Solido Variation Designerとの統合により、包括的なコーナーバリエーション結果に効率的に対応します。これにより、すべての環境コーナーにおいてより少ないシミュレーション回数で精度が得られことからより効果的な検証が可能になり、RFシミュレーションの複雑さを軽減します。

2次および3次インターセプト(IP2、IP3)、1dB圧縮点(P1dB)などの重要RF指標を比較した最近のベンチマークでは、AFS HBは厳しい精度要求を満たし、65nmから7nmまでのプロセスノードにおいて、精度設定が同等の他の市販ソリューションよりも高いシミュレーション性能を示しました。AFS HBは、ポストレイアウト設計で平均2.6倍の高速化(図3)、プリレイアウト設計で1.8倍の高速化を記録しました。最も困難なポストレイアウト・マルチトーン・シミュレーションにおいて、AFS HBは、収束して正確な結果を得ることができた唯一のソリューションでした。

まとめ

HPC、通信、自動運転、IoTなどの技術革新により半導体設計の複雑さが増大するなか、それを凌ぐ速さで設計イノベーションが進んでいます。無線周波数(RF)技術は日常のあらゆる場面で使われるため、通信分野でのイノベーションは特に顕著です。RF技術は、現代の先進的エレクトロニクス製品の多くの側面で重要な役割を果たしています。シリコンの製造前にこれらの設計を適切に検証するには、シリコンの動作を正確に予測する特殊なRF解析が必要です。

難易度の高いナノメータ・アナログ/RF/ミクスドシグナル回路の検証のために、Analog FastSPICEプラットフォームは、精度が高く、包括的、かつ高性能な検証機能を単一のプラットフォームで提供します。またその精度は、高度なプロセスジオメトリで世界の主要ファウンドリの認定を受けており、日常生活のあらゆる場面を支えるRF技術に対応します。

シーメンスEDAのアナログ/ミクスドシグナル回路シミュレーションのシニアプロダクトマネージャー。EDAソフトウェア業界で25年以上の経験を有しており、シーメンスEDAに参加する前は、ケイデンスとシノプシスで勤務していました。カーティスは、ヒューズ・エアクラフト・カンパニーで高速信号検出受信機のアナログおよびRF回路設計者としてキャリアをスタートさせました。 イリノイ大学でBSEEの学位を取得しています。

シーメンスEDAのAMS シミュレータおよびデザインプラットフォーム製品を担当するアカウント・テクノロジー・マネージャー。2017年に入社、ソリューションアーキテクチャとしてRFカスタマーエンゲージメントと製品開発に専念しました。2021年には日本に異動し、顧客のAMS問題の解決に貢献しています。 シーメンスEDA入社以前は、シニア回路設計者として、RF/ミリ波アプリケーション製品の開発に従事していました。台湾 国立清華大学にてMSEE取得。

notebook-laptop

notebook-laptop